Product Summary

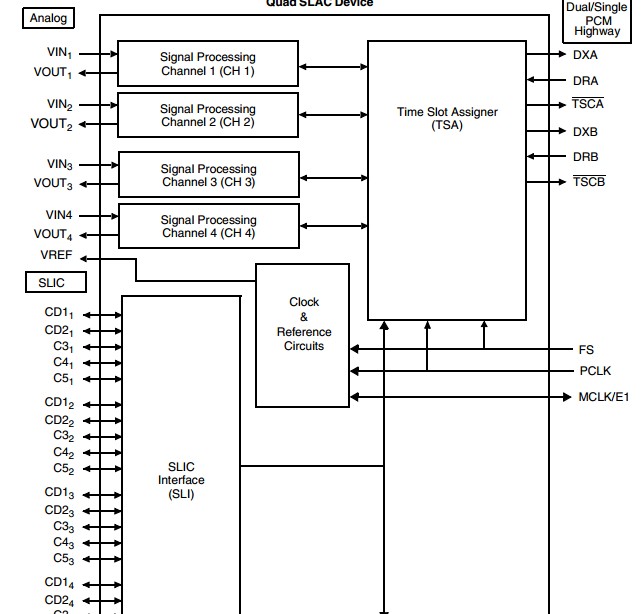

The AM79Q021VC Quad Subscriber Line Audio-Processing Circuit (QSLAC) devices integrate the key functions of analog linecards into high-performance,very-programmable, four-channel codec-filter devices. The AM79Q021VC is based on the proven design reliable SLAC device families of the Legerity. The advanced architecture of the AM79Q021VC implements four independent channels and employs digital filters to allow software control of transmission, thus providing a cost-effective solution for the audio-processing function of programmable linecards.

Parametrics

AM79Q021VC absolute maximum ratings: (1) Storage Temperature: -60°C<TA<+125°C; (2) Ambient Operating Temperature: -40°C<TA<+85°C; (3) Ambient Relative Humidity: 5% to 95%; (4) VCCA with respect to AGND: -0.4V to +7.0V; (5) VCCA with respect to VCCD: ±50mA; (6) VCCD with respect to DGND: -0.4V to +7.0V; (7) Vin with respect to AGND: -0.4V to (VCCA +0.4V) ; (8) AGND with respect to DGND: ±0.4V; (9) Source from VCCD: 40mA; (10) Sink into DGND: 40mA; (11) Latch-up immunity (any pin) : ±100mA; (12) Ambient Temperature: 0°C<TA<70°C.

Features

AM79Q021VC features: (1) Performs the functions of four codec/filters; (2) Software programmable: SLIC input impedance, Transhybrid balance, Transmit and receive gains,Equalization (frequency response) , Digital I/O pins, Programmable debouncing on one input, Time slot assigner, Programmable clock slot and PCM transmit clock edge options; (3) Standard microprocessor interface; (4) A-law, μ-law, or linear coding; (5) Single or Dual PCM ports available: Up to 128 channels (PCLK at 8.192MHz) per PCM port,Optional supervision on the PCM highway; (6) 1.536, 1.544, 2.048, 3.072, 3.088, 4.096, 6.144, 6.176, or 8.192 MHz master clock derived from MCLK or PCLK; (7) Built-in test modes with loopback, tone generation, and μP access to PCM data; (8) Low-power, 5.0V CMOS technology; (9) 5.0V only operation; (10) Mixed state (analog and digital) impedance scaling; (11) Performance characteristics guaranteed over a 12 dB gain range; (12) Real Time Data register with interrupt (open drain or TTL output) ; (13) Supports multiplexed SLIC inputs; (14) Broadcast state; (15) 256kHz or 293kHz chopper clock for Legerity SLICs with switching regulator; (16) Maximum channel bandwidth for V.34 modem.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

AM79Q021VC |

Other |

|

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

Am79213 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79231 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79514 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79533I |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79534 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79535 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))